# 2:1 Multiplexer Design Using Lector, LCnmos, LCpmos Power Reduction Techniques with 45nm, 90nm, 180nm CMOS Technology

Dr. Ch. Manohar Kumar<sup>1</sup>, Ms. M.V. Sree Harika<sup>2</sup>, Mr. S. Mahesh Babu<sup>3</sup>, Ms. D. Manasa Lakshmi<sup>4</sup>, and Mr. G. Jagadeesh<sup>5</sup>

<sup>1</sup>Assistant Professor, Department of Electronics and Communication Engineering, Gayatri Vidya Parishad College for Degree and PG Courses(A), Visakhapatnam, Andhra Pradesh, India

<sup>2,3,4,5</sup>Student, Department of Electronics and Communication Engineering, Gayatri Vidya Parishad College for Degree and PG Courses(A), Visakhapatnam, Andhra Pradesh, India

Correspondence should be addressed to Dr. Ch. Manohar Kumar; Manohar.chebrolu@gmail.com

Copyright © 2022 Made Dr. Ch. Manohar Kumar et al. This is an open-access article distributed under the Creative Commons Attribution License, which permits unrestricted use, distribution, and reproduction in any medium, provided the original work is properly cited.

**ABSTRACT-** Today's modern communication requires high data transmission rate and low power consumption. One of the most common concept of data transmission can be achieved by Multiplexers. The Multiplexers are the logic designs where data can be transmitted by n number of inputs over transmission path based on the selection line producing the single input. The application of Multiplexers is more active in communications system. AlsoLow power consumption and high-speed result is the major concern for choosing the digital circuits [1,2].

Here we designed 2:1 Multiplexer using CMOS technology with 45nm, 90nm, 180nm. Since CMOS offers less power consumption, we can till reduce the power consumed by using power reduction techniques. In this paper we designed and compared the 2:1 Multiplexer using Lector, LCnmos and LCpmos power reduction techniques.

**KEYWORDS-** Multiplexer, CMOS technology, Lector technique, LCnmos technique and LCpmos technique.

## I. INTRODUCTION

A combinational circuit in digital electronics defines as the circuits whose output depends upon on the combinational input variables.

The combinational circuits have some of the special characteristics such as:

- no memory required

- no feedback

- 'm' number of outputs are obtained by 'n' number of combinational inputs.

Examples of common combinational logic circuits include: half adders, full adders, multiplexers, demultiplexers, encoders and decoders [3,4].

The below figure 2, represents the general block diagram representation of Combinational circuit for 'm' number of outputs for 'n' combinational inputs

Figure 1: Block diagram of combinational circuit

# **II. MULTIPLEXER**

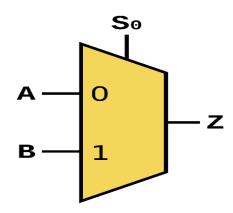

One of the most used combination circuits is the MULTIPLEXER, also known as MUX.A Multiplexer is a combinational circuit, which has  $2^n$  inputs, a single line output and n number of selection lines. The output of the multiplexer depends upon the selection lines Multiplexers are of many types i.e 2:1 mux, 4:1 mux, 8:1 mux, 16:1 mux and many more[5,6,7].

The Boolean expression for 2:1 multiplexer is given as:  $Z=A.(not)S_0+B.S_0$

Figure 2: Block diagram of 2:1 multiplexer

Multiplexer is a combinational logic circuit designed to switch one of several input lines through to a single

common output line by the application of a control signal. A 2-to-1 multiplexer consists of two inputs A and B, one select input  $S_0$  and one output Z. Depending on the select

signal, the output is connected to either of the inputs. Since there are two input signals, only two ways are possible to connect the inputs to the outputs, so one selects needed to do these operations. If the select line is low, then the output will be switched to Ainput, whereas if select line is high, then the output will be switched to B input. The below figure shows the block diagram of a 2-to-1 multiplexer which connects two 1-bit inputs to a common destination.

| Table 1: 2:1 Multiplexer truth table |

|--------------------------------------|

|--------------------------------------|

| S | Z |

|---|---|

| 0 | В |

| 1 | А |

The applications of Multiplexer can be seen in Communication Systems, Computer Memory, Telephone Network, Arithmetic logic unit, Serial to parallel converter.

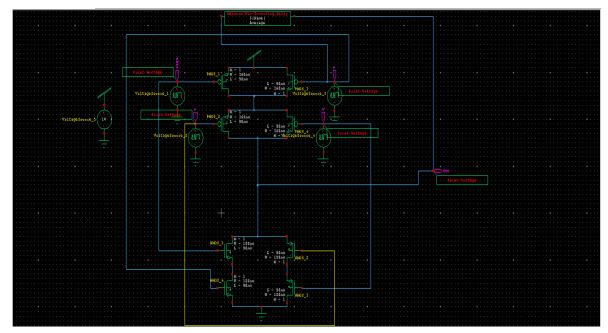

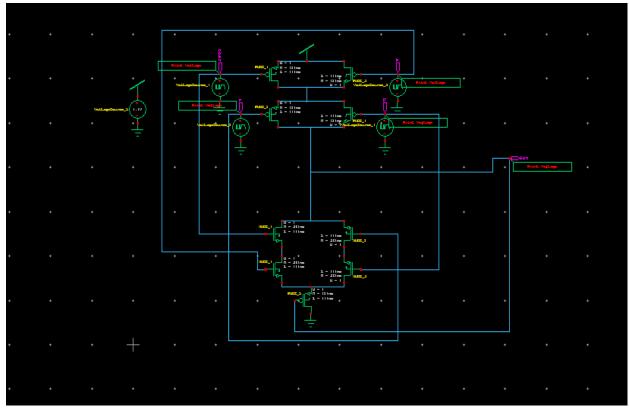

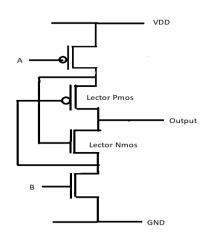

Figure 3: 2:1 Multiplexer using CMOS

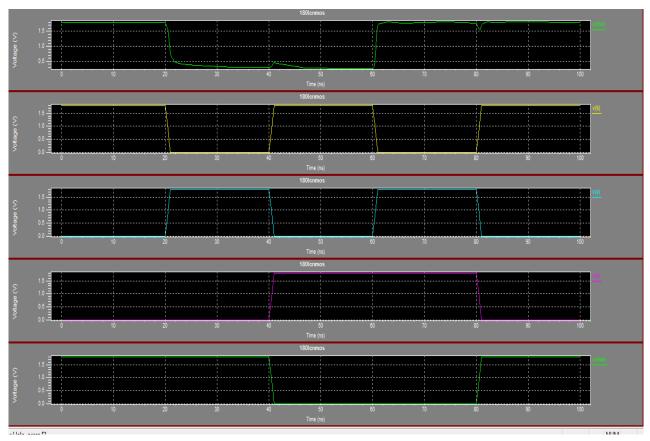

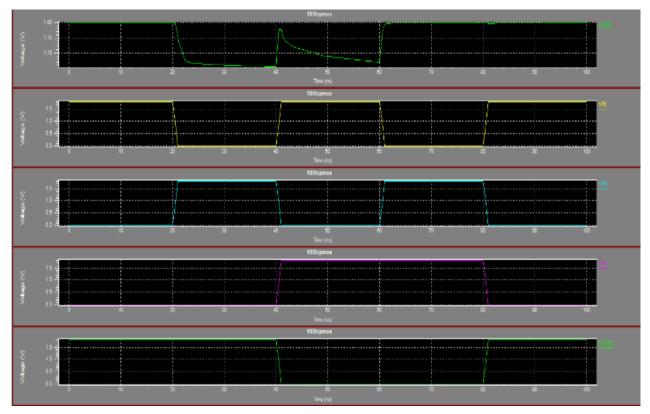

Figure 4: 2:1 Multiplexer output waveform for 180nm

Figure 5: 2:1 Multiplexer output waveform for 90nm

Figure 6: 2:1 Multiplexer output waveform for 45 nm

# **III. POWER REDUCTION TECHNIQUES**

Low power design is a necessity today in all integrated circuits. As companies, started packing more and more features and applications on the battery-operated devices, battery backup time became very important. Power consumption slowly became an increasingly important criterion from the customers. Due to this, all chip companies are focusing on lower power consumption. There are efforts to reduce dynamic as well as static power consumption. Companies started to reduce the nominal voltages inside the chip, however, this was also limited along with the technology. So a lot of low power design techniques started to get employed during the Chip Design process to reduce both static and dynamic power consumption. Here in this paper we are going to discuss the three major power reduction techniques such as Lector, LCnmos, LCpmos.

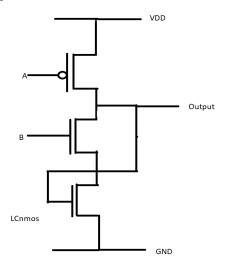

## A. L Cnmos Technique

The LCnmos is a leakage current power reduction technique in which an additional nmos is placed after the pull-down section, therefore, reducing the leakage power. It is a selfcontrolled nmos transistor, which does not require any other additional input. Only the output is feedback to the nmos[8,9].

Figure 7: CMOS inverter using L Cnmos

The above figure 7, represents the L Cnmos of the CMOS inverter. Here the inputs are A and B. The output of the

CMOS inverter is feedback to the additionally placed nmos below the pull-down.

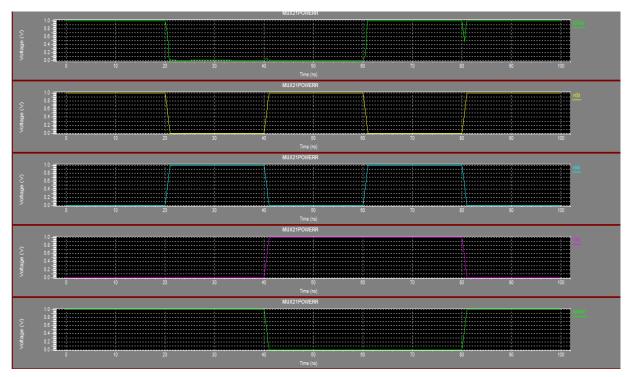

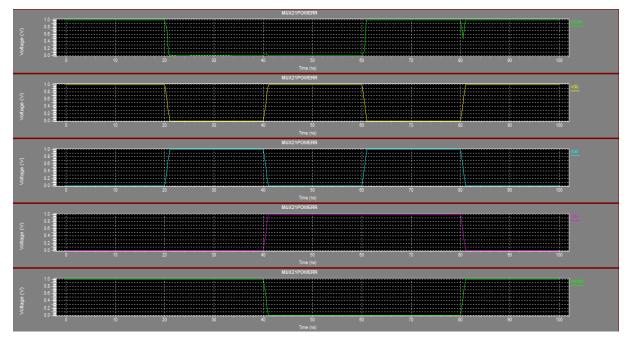

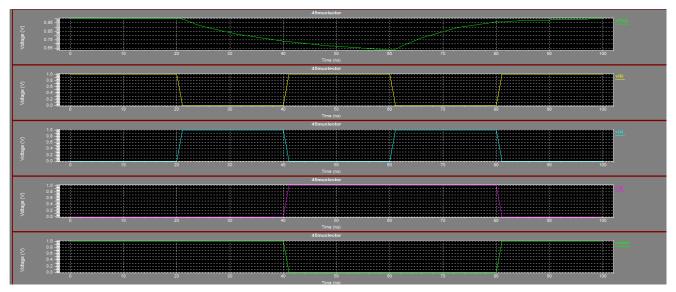

Figure 8: 2:1 Multiplexer using L Cnmos technique

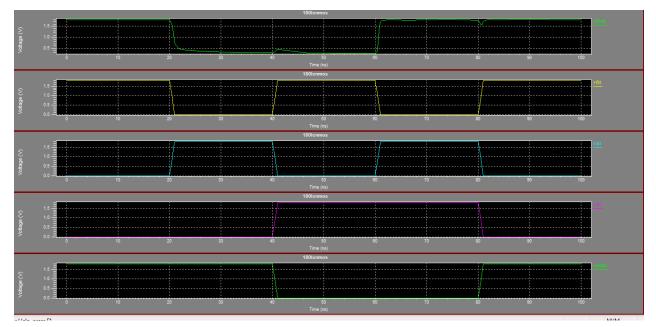

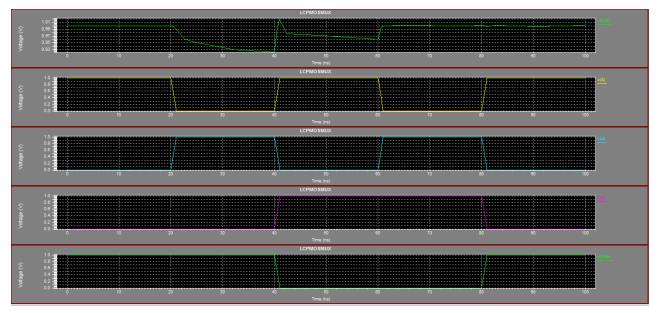

Figure 9: 2:1 Multiplexer output waveform for 180nm

Figure 10: 2:1 Multiplexer using LCnmos with 90nm

Fig.11: 2:1 Multiplexer using LCnmos with 90nm output

# B. L Cpmos Technique

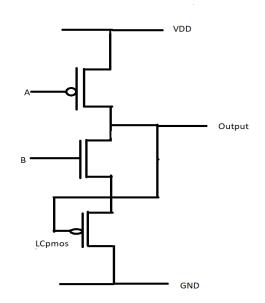

The LCpmos is a leakage current power reduction technique in which an additional pmos is placed after the pull-down section therefore reducing the leakage power. It is a selfcontrolled pmos transistor which does not require any other additional input. Only the output is feedback to the pmos[10,11].

Figure 10: CMOS inverter using L Cpmos

The above figure 10, represents the LCpmos of the CMOS inverter. Here the inputs are A and B. The output of the CMOS inverter is feedback to the additionally placed pmos

below the pull-down.

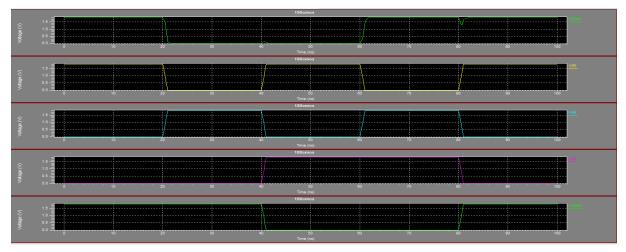

Fig.12: 2:1 Multiplexer using LCpmos technique

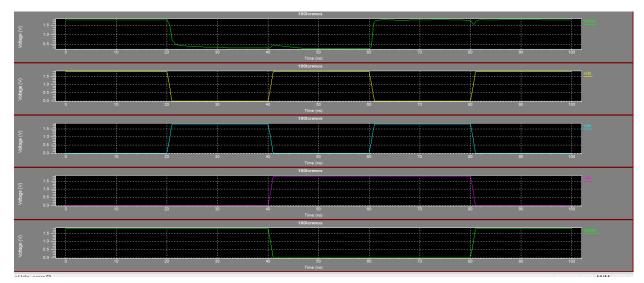

Figure 13: 2:1 Multiplexer output waveform for 180nm

Figure 14: 2:1 Multiplexer output waveform for 90nm

Figure 15: 2:1 Multiplexer output waveform for 45nm

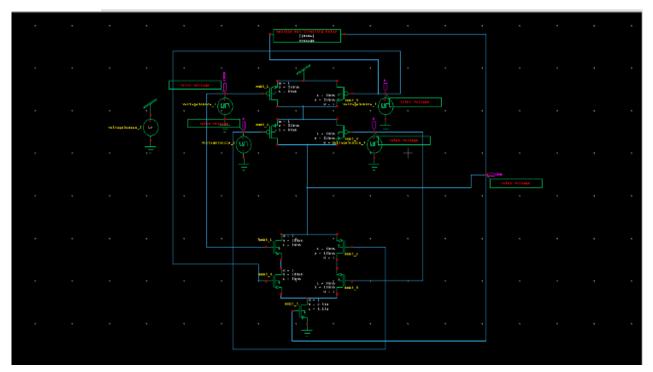

# C. Lector Technique

In this technique during standby mode, threshold voltage is elevated to a higher value by making substrate voltage either higher than supply voltage (for PMOS) or lower than ground (for NMOS)[12]. Two leakage control Transistors (LCTs) were introduced to each of thermos gates. This is done by adding a PMOS transistor to the Pull up network and a NMOS transistor to the pull-down network. The gate terminal of one the LCT is regulated by the source terminal of the other and any one of the LCTs will be in OFF state for any input given to the CMOS gate, by this an extra resistance will be formed in-between the path (from supply to ground). This decreases the sub-threshold leakage current and there by the static power is reduced.

Figure 16: CMOS inverter using Lector

Figure 17: 2:1 multiplexer using Lector technique

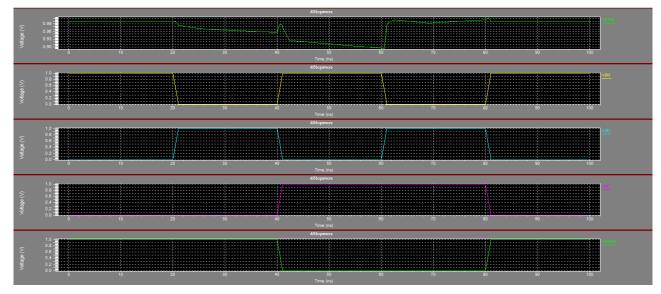

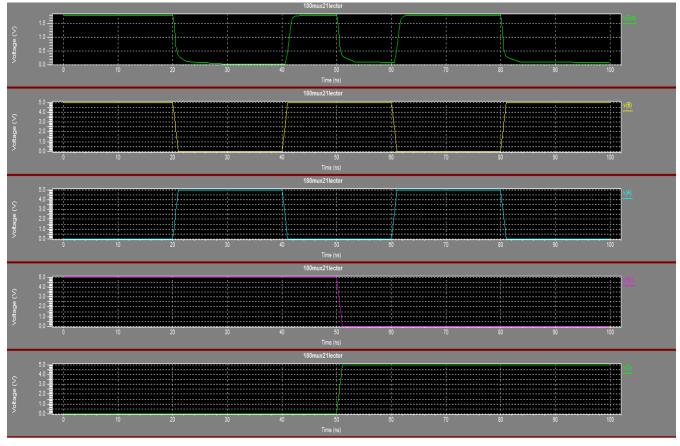

Figure 18: 2:1 Multiplexer output waveform for 180nm

Figure 19: 2:1 Multiplexer output waveform for 90nm

Figure 20: 2:1 Multiplexer output waveform for 45nm

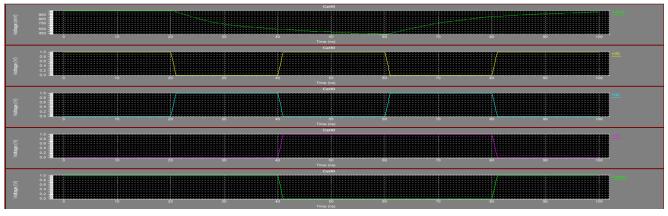

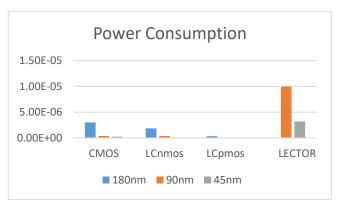

Table 2: Comparison of different power reductiontechniques with different nanometer technologies

| Technique | 180nm                                      | 90nm                                       | 45nm                                       |

|-----------|--------------------------------------------|--------------------------------------------|--------------------------------------------|

| CMOS      | 3.007123e <sup>-</sup><br><sup>006</sup> W | 3.75683e <sup>-007</sup> W                 | 2.520625e-<br>007W                         |

| LCnmos    | 1.871549e⁻<br><sup>006</sup> ₩             | 3.928740e <sup>-</sup><br><sup>007</sup> W | 2.715874e <sup>-</sup><br><sup>009</sup> W |

| LCpmos    | 3.373305e <sup>-</sup><br><sup>007</sup> W | 9.163672e <sup>-</sup><br><sup>009</sup> ₩ | 7.85727e⁻<br><sup>009</sup> W              |

| LECTOR    | 3.786099e <sup>-</sup><br><sup>009</sup> W | 9.95141e <sup>-006</sup> W                 | 3.192832e <sup>-</sup><br><sup>006</sup> W |

Figure 21: Comparison of power reduction techniques

# **IV. CONCLUSION**

The leakage power consumption is a great challenge in nano-meter scale (CMOS) technology, although previous techniques are effective in some ways, no perfect solution for reducing leakage power consumption is yet known. Therefore, based upon technology & design criteria the designers can choose the techniques. In this paper we provided few power consumption techniques that can be used for the designing of VLSI circuits. From all the mentioned power reduction techniques, LCpmos technique has very low power consumption with a power consumption value of 7.85727e<sup>-009</sup>W when compared to that of LCnmos and Lector techniques in 45nm technology. Therefore, a circuit can be designed using the LCpmos power reduction technique with 45 nm technology.

#### REFERENCES

- [1] Design and analysis of 2: 1 multiplexer circuit for high performance. Abirami, M. Arul Kumar, E. Abinaya and J. Sowmaya, "Design and analysis of 2: 1 multiplexer circuit for high performance", International Journal of Electrical and Electronics Engineers Vol., no. 7, Jan-June 2015

- [2] Design of multiplexer in multiple logic styles for low power VLSI. M. Padmaja and V. N. V. Satya Prakash, "Design of multiplexer in multiple logic styles for low power VLSI", International Journal of Computer Trends and Technology, vol. 3, no. 3, 2012.

- [3] Anugraha RV, Durga DS. Design and performance analysis of 2: 1 multiplexerusing multiple logic families at 180 nm technology. IEEE Int Conf On RecentTrends in Elect Inf Comm Tech (RTEICT) 2017:1849–53.

- [4] AGARWAL, A. et al. Leakage Power Analysis and Reduction for Nanoscale Circuits, IEEE Micro, Los Alamitos, v.26, n.2, p 68-80, Mar. 2006

- [5] N. Hanchate and N. Ranganathan," Lector: A technique for leakage reduction in CMOS circuits", IEEE Transactions on Very Large Scale Integration (VLSI) Systems, vol. 12, no. 2, pp. 196-205, February 2004.

- [6] Farzan Fallah and MassoudPedram, "Standby and active leakage current control and minimization in CMOS VLSI circuits", *IEICE*, January 2005.

- [7] Milind Gautam and ShyamAkashe, "Transistor gating: reduction of leakage current and power in full subtractor circuit", IEEE Advance Computing Conference(IACC), pp. 1514-1518, February 2013

- [8] V. K. Sharma and M. Pattanaik, "VLSI scaling methods and low power CMOS buffer circuit", *Journal of Semiconductors*, vol. 34, pp. 095001, 2013.

- [9] R. Lorenzo and S. Chaudhury, "LCNT-an approach to minimize leakage power in CMOS integrated circuits", Microsystem Technologies, vol. 23, no. 9, pp. 4245-4253, 2017.

- [10] N. Ekekwe and R. Etienne-Cummings, "Power dissipation sources and possible control techniques in ultra-deep submicron CMOS technologies", Microelectron. Journal, vol. 37, no. 851, 2006.

- [11] A. Rjoub and M. Al-Ajlouni, "Efficient multi-threshold voltage techniques for minimum leakage current in nanoscale technology", *Int. J. Circuit Theory Appl.*, vol. 39, no. 1049, 2011.

- [12] Anand N, George Joseph and Suwin Sam Oommen, "Performance Analysis and Implementation of Clock gating techniques for Low power applications", International Conference on Science, Engineering and Management Research (ICSEMR 2014) 978-1- 4799-7613-3/14/\$31.00 ©2014 IEEE.

#### **ABOUT THE AUTHOR**

**Dr. Ch. Manohar Kumar** was born in 23-08-1987. He received his B.Tech (ECE) degree from St.Ann's College of Engineering And Technology Chirala, AP, India in 2008. He received his M.Tech from Andhra University, Visakhapatnam ,AP, in the field of Radar And Microwave engineering in 2013.He received Ph.D. In the field of metamaterial Antennas,

Department of School of Engineering, Career Point University, KOTA, Rajasthan (2022). Currently, he is working as Assistant Professor in ECE dept.,Gayatri vidya Parishad college for Degree and PG Courses(A),Visakhapatnam,Ap. His research fields include Metamaterial Antennas, Micro strip Antennas, MIMO Antennas.