# A Study on High Performance Split Radix FFT

Karishma A. Deshmukh, Prof. P. R. Indurkar, Prof. Mrs. D. M. Khatri

Abstract— A high performance hardware FFT have numerous application in instrumentation and communication systems. It describes new parallel FFT architecture which combines the split-radix algorithm with a constant geometry interconnect structure. The split-radix algorithm knows to have lower multiplicative complexity than both radix-2 as well as radix-4 algorithm. The split-radix algorithm maps onto a constant geometry interconnect structure in which the wiring in each FFT stage is indistinguishable, resulting in low multiplexing overhead. We are exploiting the lower arithmetic complexity of split-radix to lower dynamic energy, by gating the multipliers during trivial multiplication. The proposed FFT accomplishes less power than a parallel radix-4 design when computing at some point, the real-valued transform.

*Index Terms*— FFT (Fast Fourier Transform), orthogonal frequency division multiplexing (OFDM), ultra-wideband (UWB).

## I. INTRODUCTION

Discrete Fourier Transform generates a fixed duration discrete frequency sequence that is obtained by sampling one period of Fourier Transform. Fast algorithms for computing the DFT which are called as fast Fourier transform (FFT). FFT computes the DFT and produces accurately the same result as calculating the DFT definition directly. The dissimilarity is that an FFT is much faster. FFT is applicable in communications. The split-radix FFT has lower complication than the radix-4 or any higher-radix power-of-two FFT.

In 2005, Y. W. Lin shows that the pipelined FFT architecture which is called as mixed-radix multipath delay feedback (MRMDF). The power consumption and hardware cost was also collect in this processor by using the higher radix FFT algorithm with less memory and complex multipliers. A novel 128-point FFT/IFFT processor for OFDM-based UWB systems was proposed. In addition, the number of complex multiplications is less effectively reduced by using a higher radix algorithm [7]. Y. Chen

K. A. Deshmukh, Student, M. Tech, Department of electronics and telecommunication Engg, BDCOE, Sewagram (wardha) Maharashtra, India, 09960559366, (e-mail deshmukhkarishma589@gmail.com)

**Prof. Mrs. D. M. Khatri**, , currently working as Assistant Professor in B.D.C.O.E., Sevagram, Department of electronics and telecommunication Engg, BDCOE, Sewagram (wardha) Maharashtra, India, 09422842999, (e-mail deepali.85@rediffmail.com).

presented a new dynamic voltage and frequency scaling (DVFS) FFT processor for MIMO OFDM applications. MIMO OFDM systems had achieved better reliability and superior capacity, the power consumption also increases because of the unlimited difficulty for the multi-stream processing. Therefore, less power becomes a major target in design of MIMO OFDM devices, especially for portable applications. To save the power of the FFT processor grows proportionally to the stream number which occupies a large percentage of system power. The dynamic voltage and frequency scaling (DVFS) is an effective technique to achieve less power. Parallelized radix-2 FFT structure has been adopted to store the power consumption [8]. In 2010 Shen-Jui Huang used the eight-data-path 2048-point FFT processor that has been proposed with a T.R. of 2.4 GS/s for OFDM-based gigabit WPAN application as well as consumed less power. Proposed work was based on split radix FFT architecture. FFT Computation can be done using different algorithm based on Radix 2, Radix 4, Radix 8, Split Radix etc. The split-radix algorithm has lesser multiplicative complexity than both radix-2 and radix-4 algorithms. The split-radix FFT mixes radix-2 and radix-4 decompositions. The split-radix FFT has lower complication than the radix-4 or any higher-radix power-of-two FFT.

# II. PARALLEL FFT ARCHITECTURE

In the previous work author focused on the pipelined FFT architecture using one or more pipelines, consisting of  $\log_r$  N stages of butterfly data-paths.

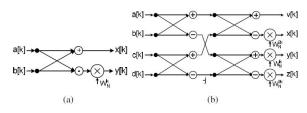

Fig. 1. Block diagram of (a) radix-2 and (b) radix-4 butterfly.

This paper describes parallel architecture with N/r butterfly data-paths. Fig. 1 shows the structure of radix-2 and radix-4 butterfly. The N-point, radix-r complex valued FFT contains N/r  $\log_r$  N butterfly operations, therefore the throughput of an FFT architecture is limited by the number of butterfly operations executed in parallel.

**Prof. P. R. Indurkar**, currently working as Associate Professor in B.D.C.O.E., Sevagram, Department of electronics and telecommunication Engg, BDCOE, Sewagram (wardha) Maharashtra, India, 09422116333, (e-mail prashantindurkar@rediffmail.com)

The row wise parallelization is used in pipelined FFTs, but it is not impossible to parallelize along a column of the SFG. The N/r butterflies are instantiated to determine one stage means one column of the FFT. One column of registers is used to register the output.

### III. SPLIT -RADIX CONSTANT GEOMETRY FFT

In the proposed FFT, a split –radix algorithm is a constant geometry interconnected structure. The profits of this structure are lower power, shorter critical path than radix-4 constant geometry architecture. The split –radix algorithm provides the advantage of smaller amount of non-trivial complex multiplication and addition than radix-2, radix-4, and radix-8 algorithm. The split-radix algorithm is based on [3] succession decomposing in an N-point DFT into an N/2-point DFT and two N/4 –point DFTs.

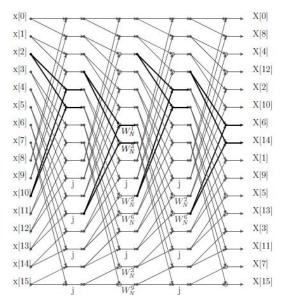

Fig 2: Rearrangement of a 16-point split-radix algorithm

$W_{N}^{k}=e^{-j2\Pi k/N}$ , this is a twiddle factor used in FFT calculation. Using a pair of radix -2-like butterflies as the basic processing unit. The split radix SFG thought of as a Cooley-Tukey radix-2 SFG, except with dissimilar twiddle factors and details in the butterflies. The split-radix SFG can be reschedule in the same way that a radix-2 Cooley-Tukey algorithm is changed into a constant geometry algorithm. The odd butterflies do not required any multipliers, while the even butterflies necessitate two due to the presence of two twiddle factors. Thus referring to these butterflies as type 1 and type 2 butterflies vary from radix-2 butterflies in two main ways. First, when the butterfly is used to determine the second half of the 4-point DFT a subtraction occurs in the top branch rather than the bottom branch. Second, butterflies are modified to calculate multiplication by  $\sqrt{-1}$  (j) without having to use the complex multiplier. This is particularly important in the split-radix design because the algorithm decreases the number of non-trivial multiplications at a cost of additional multiplications by *j*. These numbers of multiplications obtained only by non-trivial twiddle factors and by *j*.

## IV. MULTIPLIER GATING FOR SWITCHING POWER REDUCTION

The lesser multiplicative complexity of split-radix can be leveraged to reduce power. Specifically, trivial multiplications (i.e. multiplying by 1 or  $\sqrt{-1}$ ). More importantly, during bypass, the multiplier inputs should be assumed that values from the previous cycle in order to suppress switching. At one multiplier input, this is done by putting in a latch. When the multiplier is bypassed, the latch holds data from the previous cycle, otherwise the latch is clear. Like the other control signals, the latch enable signals can be controlled via minute, hard-coded lookup tables. The latches can be build-up during timing verification by forcing the enable signal to "1", in which case they add a small delay to the logic path.

The other multiplier input is controlled by tough-coded twiddle factor lookup tables. Therefore, we can modify the tables to replace "1" or " $\sqrt{-1}$ " values with twiddle factor values from the previous cycle. The net result is that during trivial multiplications, the multiplier output remains unchanged from the previous cycle, but this incorrect output is bypassed.

The proposed architecture can be extended to efficiently determine FFTs on real-valued inputs using the well-known approach described in [4]. In this approach, the even and odd samples of an *N*-point real sequence are used to form the real and imaginary parts of an *N*/2-point complex sequence. Then, an *N*/2-point complex-valued FFT is determined using the split-radix algorithm as described above. This is tracked by real-valued post-processing [6].

#### V. PROPOSED METHODOLOGY

To achieve above objective for the design of high performance split-radix FFT. The proposed methodology are design n bit Adder for addition purpose, design n bit Multiplier for multiplication, design n bit complex multiplier is used to perform complex multiplication in FFT algorithm and also design n bit split radix butterfly for generate the butterfly structure, design reorder and the storing purpose design the register.

## VI. CONCLUSION

N bit Adder is used to perform addition in FFT algorithm. CLA type of Adder is used in this design. Multiplier is used to perform real multiplication in FFT algorithm. Sequential type of multiplier has been used in these works. Complex multiplier is used to perform complex multiplication in FFT algorithm.Using the multiplier designed in the previous literatures split radix butterfly algorithm is realised. Because the split- radix algorithm is known to have lower multiplicative complexity

### International Journal of Innovative Research in Computer Science & Technology (IJIRCST) ISSN: 2347-5552, Volume-2, Issue-1, January 2014

than both radix-2 and radix-4 algorithms. It is used to generate the butterfly structure, like the upper and lower node calculations. For the reordering, the output purpose reorder block is used where reorder is register base. For output storing purpose register is used and Control block is used to control the overall system.

#### ACKNOWLEDGMENT

I wish to thank Prof.P.R.Indurkar and Prof.Mrs.D.M.Khatri for their guidance and support.

#### REFERENCES

- M. C. Pease, "An adaptation of the Fast Fourier Transform for parallel processing," Journal of the ACM, vol. 15, pp. 252–264, April 1968.

- [2] M. Corinthios, "The design of a class of Fast Fourier Transform computers," IEEE Transactions on Computers, vol. C-20, no. 6,pp.617–623, June 1971.

- [3] P. Duhamel and H. Hollmann, "Split radix' FFT algorithm," *Electronics Letters*, vol. 20, no. 1, pp. 14–16, May 1984.

- [4] H. Sorensen, D. Jones, M. Heideman, and C. Burrus, "Real-valued Fast Fourier Transform algorithms," IEEE Transactions on Acoustics, Speech, and Signal Processing, vol. 35, no. 6, pp. 849–863, June 1987.

- [5] F. Arg<sup>-</sup>uello and E. Zapata, "Constant geometry split-radix algorithms," Journal of VLSI Signal Processing, 1995.

- [6] R. Matusiak. (2001, Aug.) Implementing Fast Fourier Transform algorithms of real-valued sequences with the TMS320 DSP platform. [Online]. Available: http://focus.ti.com/lit/an/spra291/spra291.pdf

- [7] Y.-W. Lin, H.-Y. Liu, and C.-Y. Lee, "A 1-GS/s FFT/IFFT processor for UWB applications," IEEE Journal of Solid-State Circuits, vol. 40, no. 8, pp. 1726 – 1735, Aug. 2005.

- [8] Y. Chen, Y.-W. Lin, Y.-C. Tsao, and C.-Y. Lee, "A 2.4-Gsample/s DVFS FFT processor for MIMO OFDM communication systems," IEEE Journal of Solid-State Circuits, vol. 43, no. 5, pp. 1260–1273, May 2008.

- [9] S.-N. Tang, J.-W. Tsai, and T.-Y. Chang, "A 2.4-GS/s FFT Processor for OFDM-Based WPAN Applications," IEEE Transactions on Circuits and Systems II: Express Briefs, vol. 57, no. 6, pp. 451–455, June 2010

- [10] S.-J. Huang and S.-G. Chen, "A green FFT processor with 2.5-GS/s for IEEE 802.15.3c (WPANs)," in International Conference on Green Circuits and Systems, June 2010, pp. 9–13.

- [11] T. Cho, H. Lee, J. Park, and C. Park, "A high-speed low-complexity modified radix-25 FFT processor for gigabit WPAN applications," in IEEE International Symposium on Circuits and Systems, May 2011, pp. 1259–1262.

Miss. Karishma.A.Deshmukh B.E (Electronics ), Student of M Tech (II) Year(VLSI), BDCOE, Sevagram (Wardha) Nagpur University, Maharashtra, India.

**Prof. P.R.Indurkar** B.E.(Electronics and Power )M.tech(Electronics) currently working as Associate Professor,M.tech co-ordinator in B.D.C.O.E., Sevagram, Department of electronics and telecommunication Engg, BDCOE, Sewagram (wardha) Maharashtra, India, 20 years experience 09422116333, (e-mail <u>prashantindurkar@rediffmail.com</u>)

**Prof.Mrs.D.M.Khatri**, B.E.(Electronics and Power )M.tech(Electronics) currently working as Assistant Professor, in B.D.C.O.E., Sevagram, Department of electronics and telecommunication Engg, BDCOE, Sewagram (wardha) Maharashtra, India,7 years experiance 09422842999, (e-mail <u>deepali.85@rediffmail.com</u>).